Back Intel P5 (микроархитектура) Bulgarian Pentium (original) Catalan P5 (mikroarchitektura) Czech Pentium P5 Esperanto Intel Pentium French Intel Pentium (1993年) Japanese P5 (마이크로아키텍처) Korean P5 (mikroarkitektur) NB P5 (mikroarchitektúra) Slovak อินเทล P5 Thai

| |

| General information | |

|---|---|

| Launched | March 22, 1993 |

| Discontinued | July 15, 1999[1][better source needed] |

| Marketed by | Intel |

| Designed by | Intel |

| Common manufacturer |

|

| Product code | 80501 (P5) 80502 (P45C, P54CQS, P54CS) 80503 (P55C, Tillamook) |

| Performance | |

| Max. CPU clock rate | 60-300 MHz |

| FSB speeds | 50 MHz to 66 MHz |

| Cache | |

| L1 cache | 16–32 KiB |

| L2 cache | Up to 512 KiB[2] |

| Architecture and classification | |

| Technology node | 800 nm to 250 nm |

| Microarchitecture | P5 |

| Instruction set | x86-16, IA-32 |

| Extensions | |

| Physical specifications | |

| Transistors | |

| Cores |

|

| Sockets | |

| Products, models, variants | |

| Core names |

|

| Models |

|

| History | |

| Predecessor | i486 |

| Successors | P6, Pentium II, Pentium III (SSE successor) |

| Support status | |

| Unsupported | |

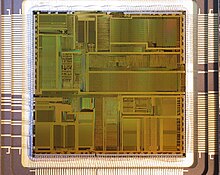

The Pentium (also referred to as the i586) is a x86 microprocessor introduced by Intel on March 22, 1993. It is the first CPU using the Pentium brand.[3][4] Considered the fifth generation in the 8086 compatible line of processors,[5] its implementation and microarchitecture was internally called P5.

Like the Intel i486, the Pentium is instruction set compatible with the 32-bit i386. It uses a very similar microarchitecture to the i486, but was extended enough to implement a dual integer pipeline design, as well as a more advanced floating-point unit. The former is something that had been argued being impossible to implement for a CISC instruction set, by certain academics and RISC competitors.[who?]

The P5 Pentium is the first superscalar x86 processor, meaning it was often able to execute two instructions at the same time. Some techniques used to implement this were based on the earlier superscalar Intel i960 CA (1989), while other details were invented exclusively for the P5 design. Large parts were also copied from the i386 or i486, especially the strategies used to cope with the complicated x86 encodings in a pipelined fashion.[6] Just like the i486, the Pentium used both an optimized microcode system and RISC-like techniques, depending on the particular instruction, or part of instruction.

Other central features include a redesigned and significantly faster floating-point unit, a wide 64-bit data bus (external as well as internal), separate code and data caches, and many other techniques and features to enhance performance.

The P5 also has better support for multiprocessing compared to the i486, and is the first x86 CPU with hardware support for it similar to IBM mainframe computers. Intel worked with IBM to define this ability and also designed it into the P5 microarchitecture. This ability was absent in prior x86 generations and x86 processors from competitors.

In order to employ the dual pipelines at their full potential, certain compilers were optimized to better exploit instruction level parallelism, although not all applications would substantially gain from being recompiled. The faster FPU always enhanced floating point performance significantly though, compared to the i486 or i387. Intel spent resources working with development tool vendors, ISVs and operating system (OS) companies to optimize their products.

In October 1996, the similar Pentium MMX[7] was introduced, complementing the same basic microarchitecture with the MMX instruction set, larger caches, and some other enhancements.

Competitors included the superscalar PowerPC 601 (1993), SuperSPARC (1992), DEC Alpha 21064 (1992), AMD 29050 (1990), Motorola MC88110 (1991) and Motorola 68060 (1994), most of which also used a superscalar in-order dual instruction pipeline configuration, and the non-superscalar Motorola 68040 (1990) and MIPS R4000 (1991).

Intel discontinued the P5 Pentium processors (sold as a cheaper product since the release of the Pentium II in 1997) in early 2000 in favor of the Celeron processor, which had also replaced the 80486 brand.[1]

- ^ a b "Product Change Notification #777" (PDF). Intel. February 9, 1999. Archived from the original (PDF) on January 27, 2000. Retrieved October 14, 2019.

- ^ "Intel® Pentium® Processor with MMX™ Technology 200 MHZ, 66 MHZ FSB - Product Specifications".

- ^ View Processors Chronologically by Date of Introduction, Intel, retrieved August 14, 2007

- ^ Intel Pentium Processor Family, Intel, retrieved August 14, 2007

- ^ I.e. 8086/88, 186/286, 386, 486, P5

- ^ as compared to a simple RISC processor like the i960.

- ^ officially known as Pentium with MMX Technology